Notice

Recent Posts

Recent Comments

Link

- [블로그] 전자과 공대생 블로그(전자회로)

- [블로그] 전자과 공대생(전자기학)

- [블로그] 배고픈 대학원생 (RF 아날로그)

- [블로그] 나라발전 교수님 (아날로그)

- [블로그] 전자과 숩달씨 ( 아날로그 회로 Razavi…

- [VOD] IDEC 아날로그회로 - 고형호 교수님 (충…

- [VOD] IDEC 아날로그회로2

- [VOD] IDEC 아날로그회로3 - 이강윤 교수님(성…

- [VOD] IDEC 아날로그회로 직관적해석 - 심재윤 …

- [VOD] IDEC 아날로그 LNA - 고형호 교수님 …

- [VOD] IDEC 아날로그집적회로 실습

- [VOD] Cadence OPAMP Verificati…

- [VOD] IDEC Full-Custom Flow 교육…

- [VOD] IDEC RF System-유형준 교수님(K…

- [VOD] IDEC 디지털 Cell-based 설계

- [VOD] IDEC PLL

- [VOD] IDEC CentOS 7 (Linux)

- [VOD] Band Gap Reference 정리

- [강의] 회로설계 멘토 삼코치

- [강의] OpAmp > CMFB

- [강의] 변박사님 : OpAmp, Radar

- [강의] PMIC - 박병하 교수님 (유료)

- [강의] 삼코치 -아날로그 회설 직무 (유료)

합법적사기꾼지망생

9.1.6 Duality of Reflection Coefficient 발진 판별법(feat. OscTest vs. OscPort) 본문

A2-4_능동초고주파 회로설계입문/Oscillator

9.1.6 Duality of Reflection Coefficient 발진 판별법(feat. OscTest vs. OscPort)

평범한 민석이 2023. 11. 19. 02:421. 측정저항의 중요성

측정저항에 따라서 LoopGain이 달라진다. 그래서 측정저항이 어떠한 값이냐에 따라, 직렬발진이 잡힐 수도 있고, 혹은 병렬발진이 보일 수가 있다.

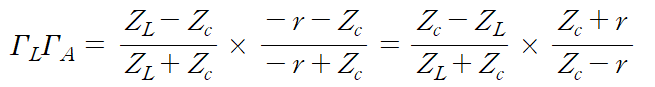

2. Loop Gain 식 and Duality

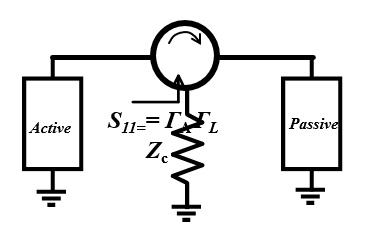

(1) 직렬발진

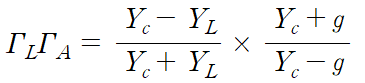

위를 그래프로 그리면 아래와 같다.

즉 직렬발진을 보려면 충분히 Zc가 커야한다.

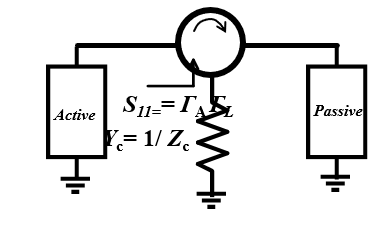

(2) 병렬발진

위를 그래프로 그리면 아래와 같다.

즉 병렬발진을 보려면 충분히 Zc가 작아야한다.

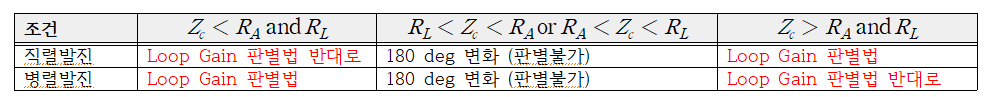

3. Duality of Reflection Coefficient 발진 판별법

:임피던스 및 어드미턴스 발진 판별법으로 추가 검증을하면 좋다. *참조

4. OscTest 다는방법

(1) 직렬

(2)병렬

5. OscPort란?

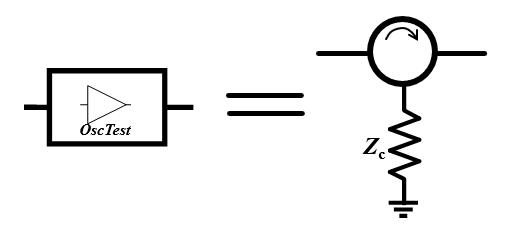

(1) OscTest

OscTest는 Small-signal simulation(ex. s-param)을 돌릴 때 사용

(2) OscPort

OscPort는 Large-signal simulation(ex. harmonic balance)을 돌릴 때 사용

*참조

*9.1.2 발진(Oscillation)의 종류 및 판별 : One-port point of view의 확장(Razavi, Pozar) ... 소신호 & 대신호 관

0. 발진을 보자 우선 소신호 관점에서 Negative Resistance가 나오고 해당 지점에서 Reactance가 0이면 발진한다는 정도는 알고 있을 것이다. 그런데 과연 그게 전부일까? 좀 더 시각을 넓혀보자 우선 몇

tgs05016.tistory.com

'A2-4_능동초고주파 회로설계입문 > Oscillator' 카테고리의 다른 글

| Colpitts 발진기 정리 사이트 (0) | 2023.12.04 |

|---|---|

| *9.1.2.α Compressed Smith Chart를 통한 직렬/병렬 발진 판별 (0) | 2023.11.22 |

| 9.1.5 Reflection Coefficient 발진 판별법(feat. OscTest) (0) | 2023.11.19 |

| 9.0.3 Stable Oscillation(정상상태발진) vs. Unstable Oscillation 발진이 개!같은 이유 (0) | 2023.11.17 |

| 9.1.4 직렬 병렬 발진 판별시 Port 다는 방법(Term) (1) | 2023.11.17 |

Comments