- 전자과 공대생 블로그(전자회로)

- 전자과 공대생 블로그2(전자기학)

- 배고픈 대학원생 (RF 아날로그)

- 나라발전 교수님 (아날로그)

- [VOD] IDEC 아날로그회로 - 고형호 교수님 (충…

- [VOD] IDEC 아날로그회로2

- [VOD] IDEC 아날로그회로3 - 이강윤 교수님(성…

- [VOD] IDEC 아날로그회로 직관적해석 - 심재윤 …

- [VOD] IDEC 아날로그 LNA - 고형호 교수님 …

- [VOD] Cadence OPAMP Verificati…

- [VOD] IDEC Full-Custom Flow 교육…

- [VOD] IDEC RF System-유형준 교수님(K…

- [VOD] IDEC 디지털 Cell-based 설계

- [VOD] IDEC PLL

- [VOD] IDEC CentOS 7 (Linux)

- [VOD] Band Gap Reference 정리

- [강의] 회로설계 멘토 삼코치

- [강의] OpAmp > CMFB

- [강의] 변박사님 : OpAmp, Radar

- [강의] PMIC - 박병하 교수님 (유료)

- [강의] 삼코치 -아날로그 회설 직무 (유료)

합법적사기꾼지망생

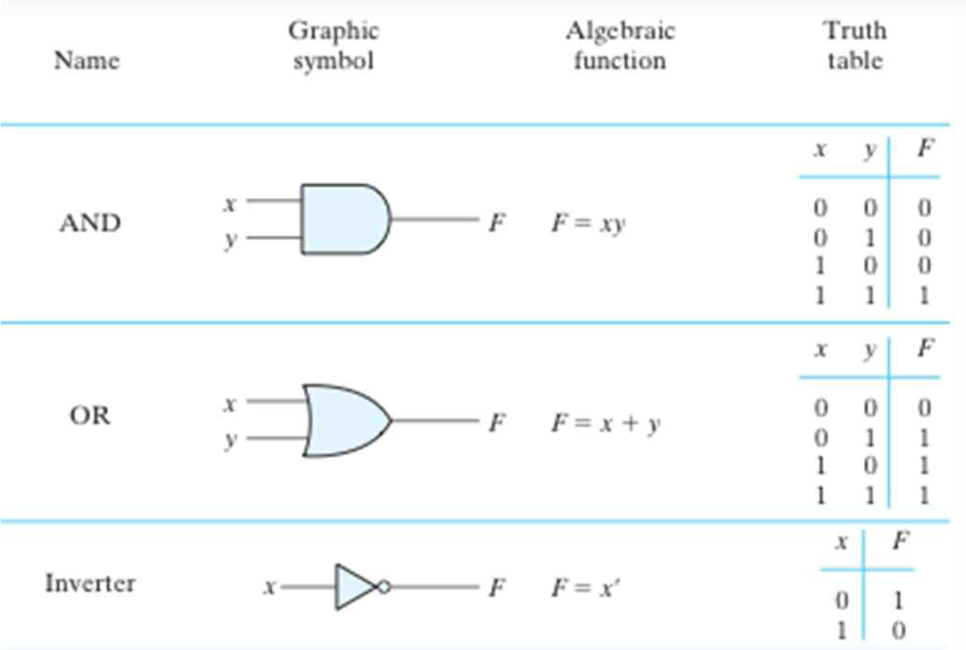

Ch2 boolean algebra and logic gates 본문

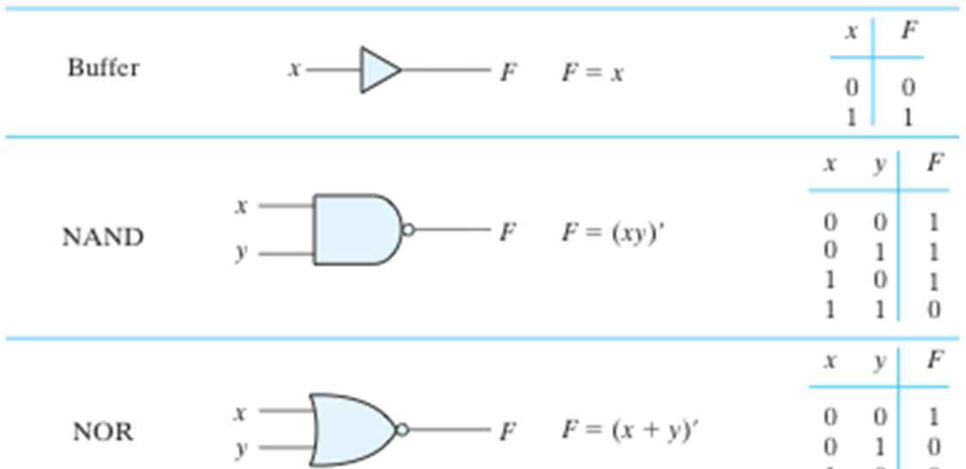

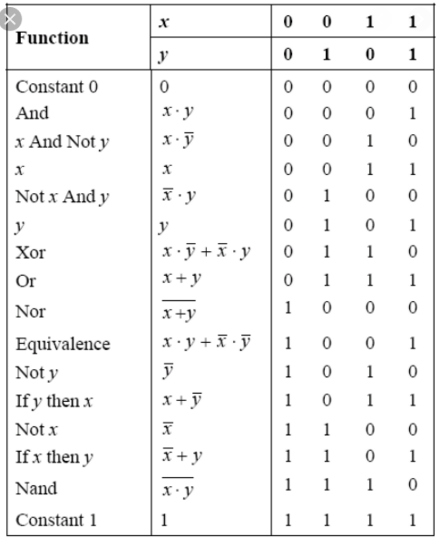

게이트

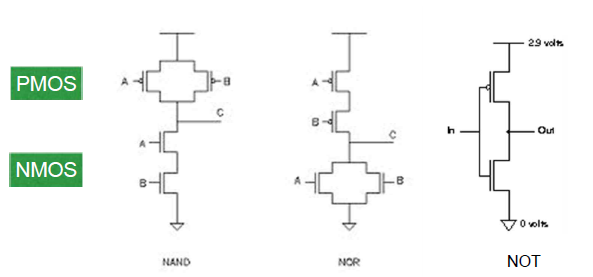

digital 2진법 신호 처리는 게이트로 이루어 지는데 이런 게이트는 트랜지스터로 이루어져 있다. switch역할로 트랜지스터가 사용되는데 NMOS와 PMOS두가지가 있다.

NMOS 트랜지스터는 G에 양전압이 Vt이상 가해지면 D에서 S로 전류가 흐를 수 있는 것이다.

NMOS 트랜지스터

NMOS트랜지스터 의 구조

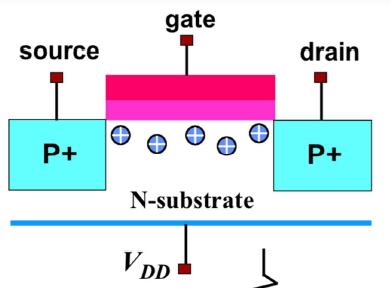

PMOS는 NMOS의 반대이다 Vt보다 작은 전압(절대값은 더큰 전압)이 G에 걸리면 D에서 S로 전류가 흐른다.

PMOS 트랜지스터

PMOS의 구조

이런 PMOS와 NMOS를 통해 기본적인 게이트 NAND NOR NOT게이트를 만들수 있다.

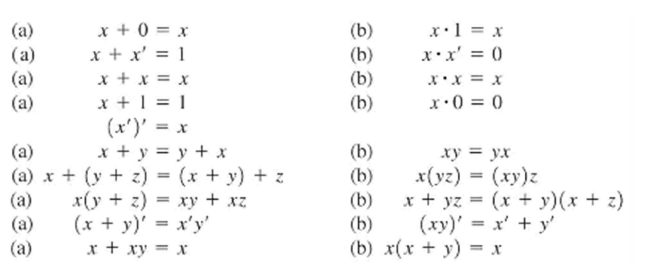

암기하면 도움되는 수식

추가적으로 알아야 하는 수식, 분배법칙~!!

(X*Y)' = X'+Y'

(X+Y)' = X'*Y'

tip for 최적화

X+X' = 1

A(X+X') =X

tip for only NAND, NOR gate

not AND = NOR , AND not = NAND

not OR = NAND , OR not = NOR

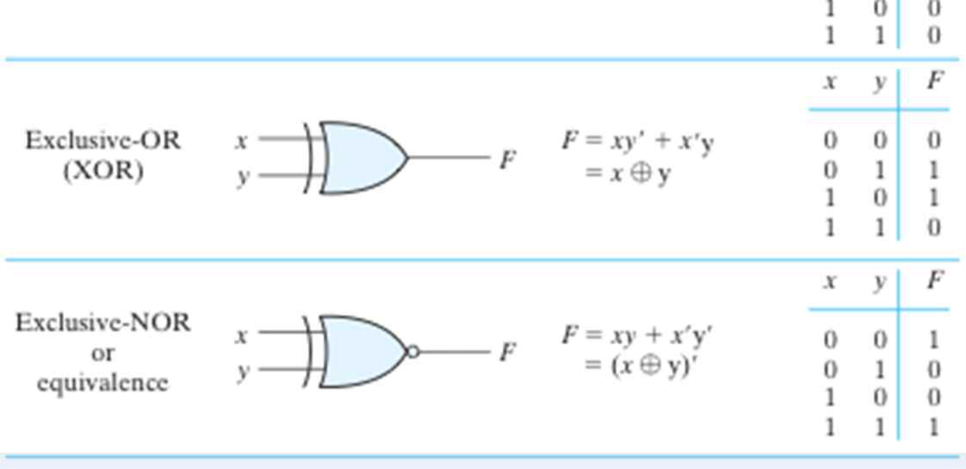

참고로 XOR게이트는 복잡한 수식들이 있는데 그건 다음과 같다.

• X*Y' + X'*Y = X ⊕ Y

• X ⊕ 0 = X

• X ⊕ 1 = X’

• X ⊕ X = 0

• X ⊕ X' = 1

• X ⊕ Y' = (X ⊕ Y)’

• X' ⊕ Y = (X ⊕ Y)’

• A ⊕ B = B ⊕ A

• (A ⊕ B) ⊕ C = A ⊕ (B ⊕ C) = A ⊕ B ⊕ C (교환법칙)

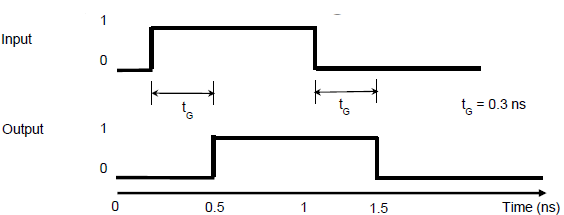

Delay(지연)

실제 물리세계에서 게이트는 입력값이 바로 즉시 출력값에 0초만에 적용되지않고 일정 Delay를 가진다.

Propagation delay : delay between an input chage and the output change

즉 다음 그래프에서 tG가 해당된다.

<참고>

#fan-in : 입력의 갯수

#fan-out : 출력의 갯수

나타내는 방법

ex. 입력 X가 4bit라면

fan -in 이 4이고 X[3:0]로 표현하거나

그림에서 X가 흐르는 도선 위에 /(슬래시)를 긋고 슬래시 위에 4를 적는다.

Gate들의 트랜지스터레벨분석

'B1_디지털시스템 공학(velilog)' 카테고리의 다른 글

| Ch4-2 more combination circuit (arith metic units) (0) | 2019.10.08 |

|---|---|

| Ch4 combinational logic design_Decoder/ Multiplexer (0) | 2019.10.08 |

| Ch2~3 회로그리기 이론적배경1 (0) | 2019.10.08 |

| Ch1 binary numbers (0) | 2019.10.08 |

| 디지털 시스템 목차, Ch0 Digital & Analog (0) | 2019.10.08 |