합법적사기꾼지망생

Ch5 Sequential circuit design_1 Flipflop 본문

Sequential 회로 vs Combination 회로

Combinational circuit이 다음과 같이 그냥 input에 의해 output이 feedback 없이 결정되는 y=f(x)함수 같은 거라면

Sequential circuit은 input output 말고 feedback이 존재한다. 그리고 이를 위해서 flip flop(혹은 latch)라는 것이 일시적인 memory(=Storage element) 역할을 한다.

그러면서 Storage element의 State(상태)를 정의하는 값 Q(t)가 존재하다. 그리고 t는 time(s)이다.

입력값 출력값또한 t라는 정의역이 들어간다.

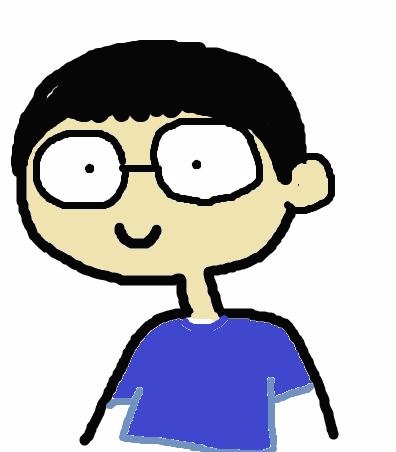

Sequential circuit은 Synchronous sequential circuit과 Asynchoronous sequential circuit 이렇게 2가지가 존재하는데

전자는 비연속적인 시간에 순간적으로 반응을 한다. 후자는 입력값이 바뀌는 연속적인 시간동안 반응한다.

우리는 주로 Sequential circuit중에서 Synchronous sequentail circuit만을 주로 사용하고 Clk이라는 값 이 들어가는 Clocked Sequential Circuit을 주로 사용한다. 이때 Clk 값은 일정한 주기를 가지고 맥박같은 입력pulse을 가진다. 그리고 Storage element 는 오직 각각의 pulse에서만 영향을 받는다.

그리고 우리는 그때 주로 Flip flops 이라는 element를 주로 Storage 로 이용한다.

Flipflop에 대해 자세히 알기 위해서 그전에 Latch에 대해 알아보자.

FlipFlop(=ff)는 주로 Latch(ff의 가장 기본적인 형태) 2개이상의 조합으로 이루어진다.

기본적인 SR Latch는 다음과 같다. 아직은 Clk값(혹은 Contol)이 들어가지 않은 상태이다.

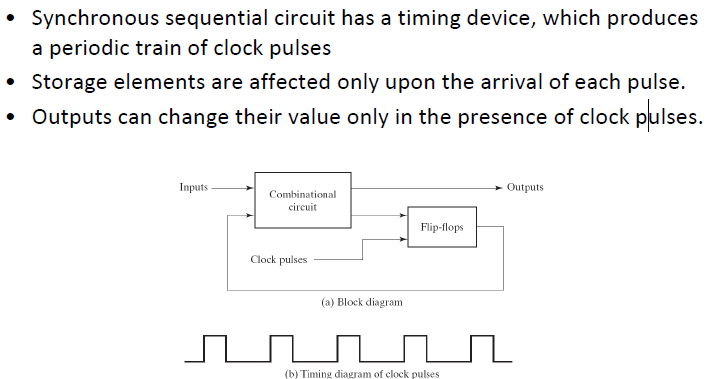

만약 여기서 Contol 값이 들어가면 다음과 같이 된다.

SR Latch with Clk

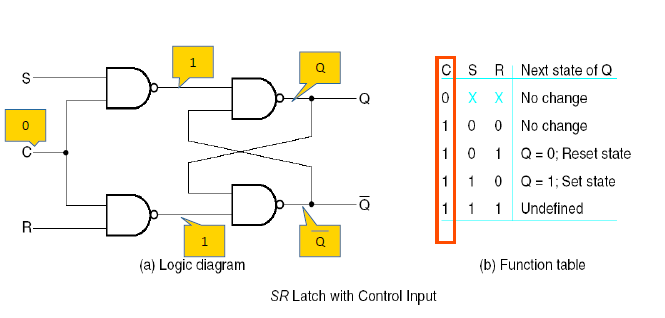

추가적으로 D Latch도 알아보자(이건 D flip flop을 만드는데 활용된다.) 이때 바로 Contol(for Clk)을 넣은 상태로 만들면 다음과 같다.

혹은 Transmission Gate를 이용하면 다음과 같다.

이제 Flip Flop으로 다시 돌아가 보자 그를 위해서 Latch 와 FF을 비교해보자.

Latch는 Contol 값이 1이기만 하면 Q(t)(혹은 state)값이 계속 변한다. 하지만 Flipflop은 오직 control이 값이 변하는 pulse라는 찰나의 순간에만 Q(t)값이 변한다. 그를 위해서 FlipFlop은 2개의 Latch로 구성된다.

Latch는 기본적으로 문제가 많은 부품이다.

예를들어 위 사진과 같은 D latch가 설계되었을때 Latch 특성상 C가 1이면 그동안 Dlatch는 작동한다

C가 1인 순간 Y(t)가 0에서 Q'(t)에 의해서 바로 1로 바뀐다. 그리고 Y(t)는 바로1의 값을 가지고 그와 동시에 바로 D(t)가 0이기 때문에 Y(t)는 또다시 0이어야한다. 그러면 Y(t)는 0이자 1을 동시에 2값을 가져야한다. 하지만 우리가 원하는 값은 Y(t)가 1 Clock pulse동안 1번만 변하는 것ㅇ르 원한다. 그래서 우리는 이를 위해서 flip flop을 쓴다. 그런데 이때 방법이 2가지가 있다

바로 a master-slave flip-flop과 an edge-triggered flip-flop이다.

a master-slave flipflop은 Clock이의 pulse가 없을때에만 FF의 값이 변한다.

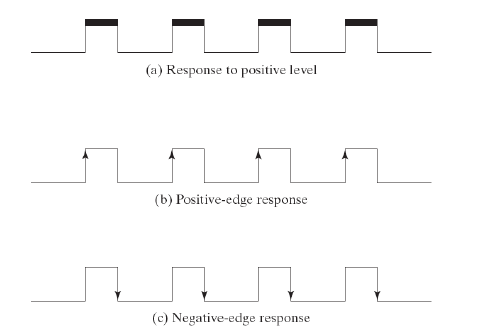

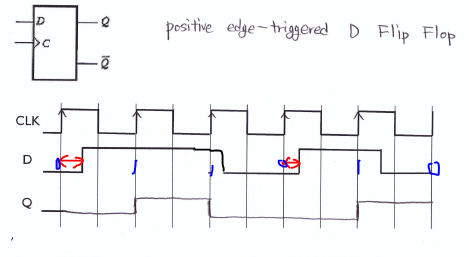

그리고 an edge-triggered flip-flop은 다음사진에 (b),(c)처럼 값이 오르거나 내리는 경우에만 state가 변하는 ff을 의미한다.

(참고로 (a)는 Latch다)

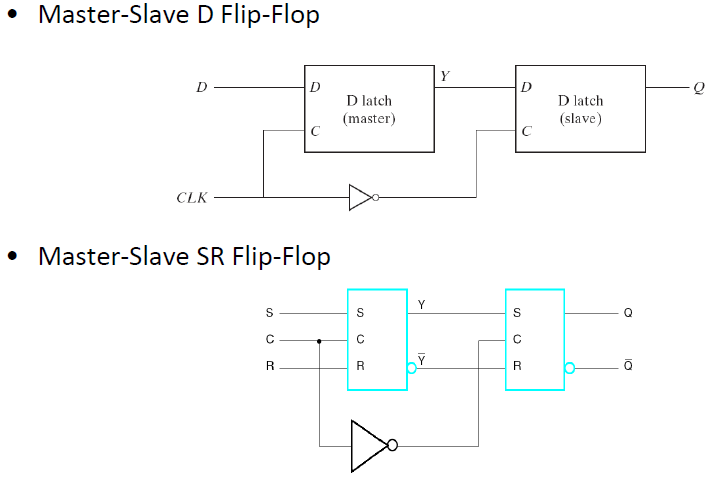

Master - slave flipflop의 구조는 다음과 같다.

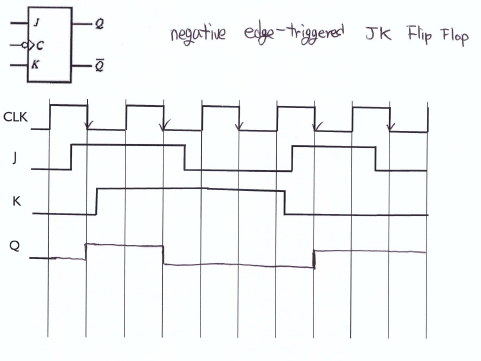

추가로 SR flipFlop은 S=1,R=1인경우가 정의 안되어있는데 그걸 보안한게 JK flipflop이다.

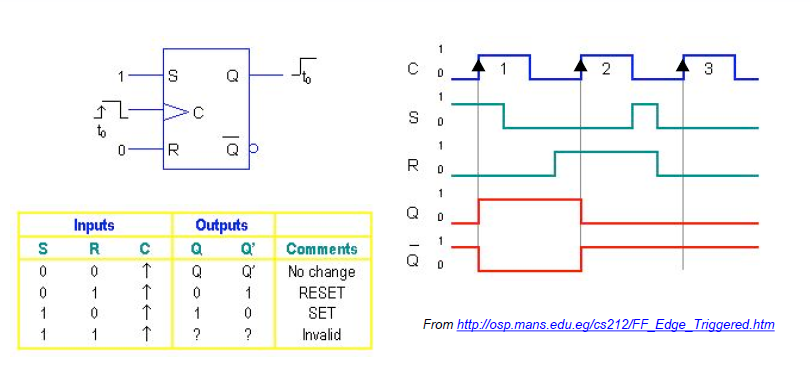

그다음으로 an edge-triggered flip-flop구조는 다음과 같다.

추가적으로 FF에는 setup time과 hold time, propagation time이 존재한다 그 정의는 다음과 같다

Hold time 은 Clock dege 이후에 input이 값을 유지해야하는 시간

setup time은 Clock transition이 생기기전에 input 값을 유지해야하는 시간

propagation delay는 입력이 clock edge 이후에 출력 될때까지 걸리는 시간

이때 Sequential circuit의 total delay는 setup time + propagation delay + combinational circuit delay 이다.

그다음으로 FF의 truth table 이다.

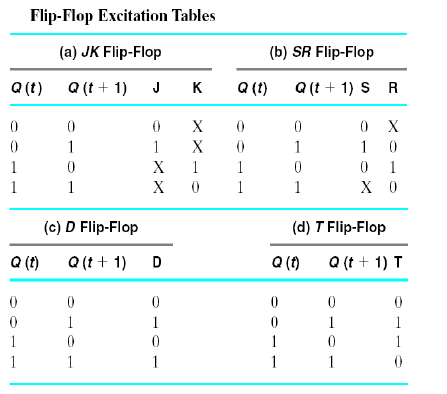

참고로 FF Excitation Table도 암기해야한다.

Tip) 각각 flip flops들에 대해서 timing diagram을 그릴 수 있어야 한다.

*중요한 참고 설명 : 위 그림에서 빨간 부분은 input(t)-to - D(t)combination circuit delay다 저거 덕분에 Q(t+1)가 D(t) 바로 다음 pulse에 반응하는 것이다.

'B1_디지털시스템 공학(velilog)' 카테고리의 다른 글

| Ch6 registers & counters(수정중) (0) | 2019.10.08 |

|---|---|

| Ch5_2 sequential circuit design(실전편) (0) | 2019.10.08 |

| Ch4-2 more combination circuit (arith metic units) (0) | 2019.10.08 |

| Ch4 combinational logic design_Decoder/ Multiplexer (0) | 2019.10.08 |

| Ch2~3 회로그리기 이론적배경1 (0) | 2019.10.08 |